Active 7 years 8 months ago. Combinational Logic Design-- Combinational Logic Design -- ESD book figure 24 -- by Weijun Zhang 042001 -- -- A simple example of VHDL Structure Modeling -- we might define two components in two separate files -- in main file we use port map statement to instantiate -- the mapping relationship between each components -- and the entire circuit.

Vhdl Structural Modeling Style

Vhdl Structural Modeling Style

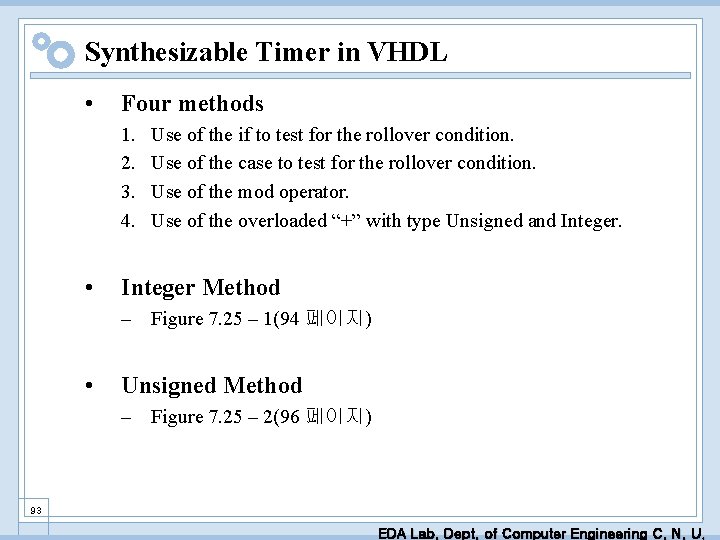

We can use generics to configure the behaviour of a component on the fly.

Define component vhdl. I have created a divided with core generator. Component instantiation is like plugging a hardware component into a socket in a board Fig. A VHDL design description written exclusively with component instantiations is known as Structural VHDL.

In VHDL-93 the component name may be followed by the keyword is for clarity and consistancy. It creates a component like the following. In VHDL generics are a local form of constant which can be assigned a value when we instantiate a component.

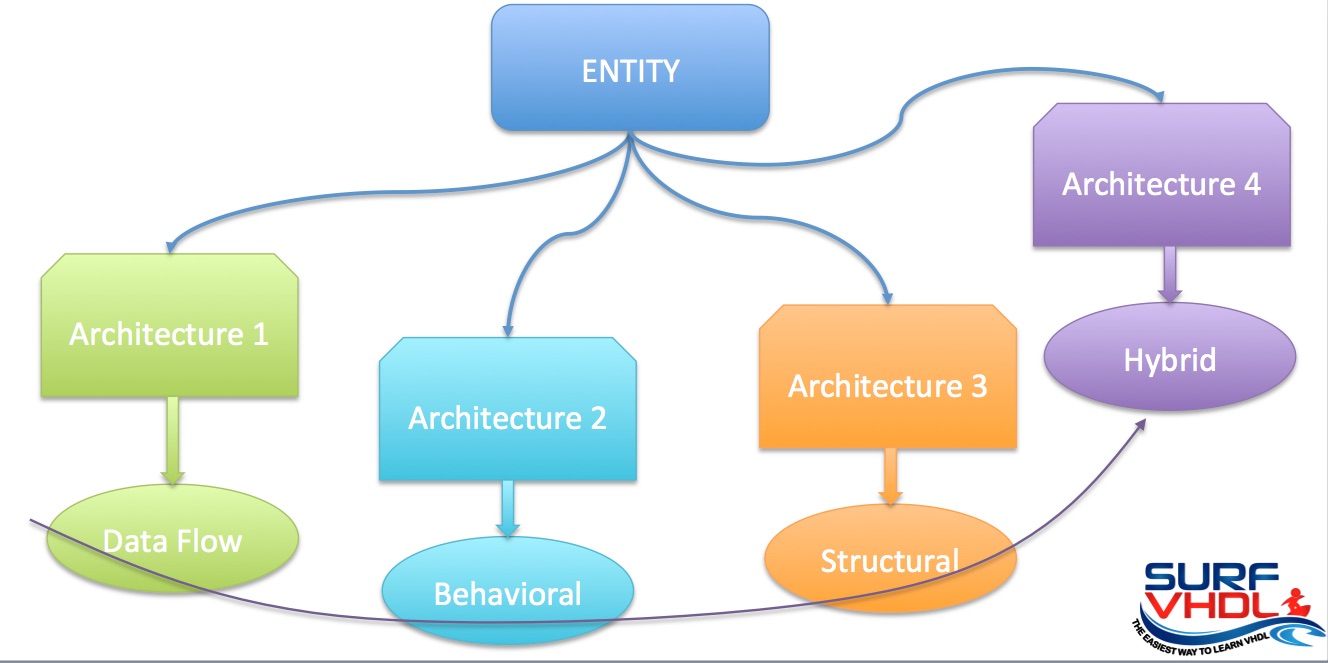

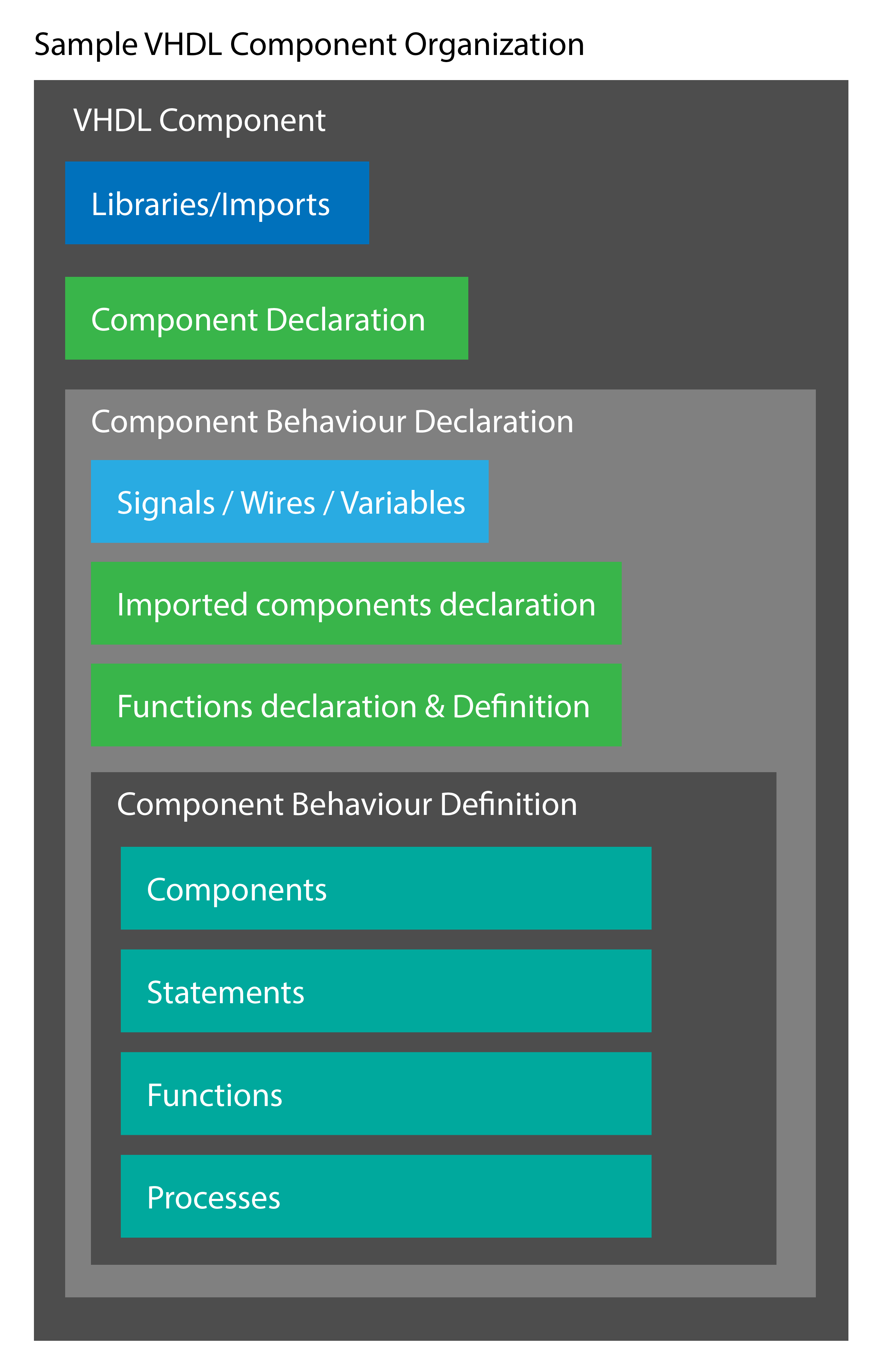

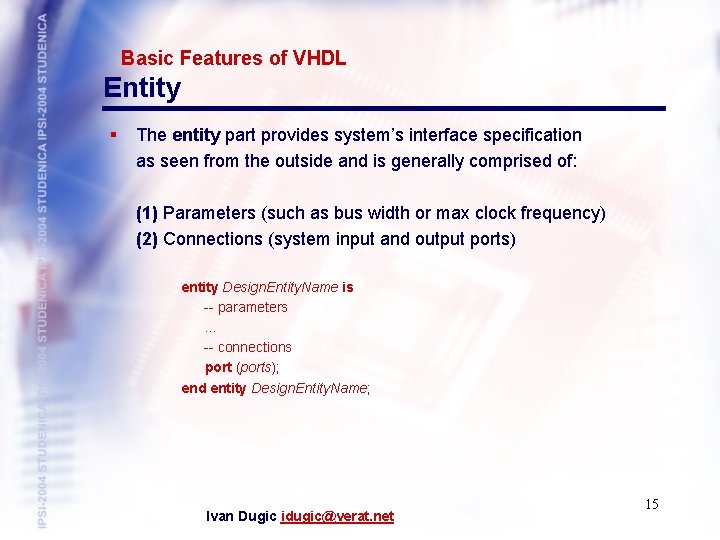

Instead of coding a complex design in single VHDL Code. The entity defines the external interface to the VHDL component we are designing including a definition of the inputs and outputs. The component declaration defines the virtual interface of the instantiated design entity the socket but it does not directly indicate the design entity.

It essentially holds the same information as the circuit netlist does. Component divider_core port clk. The rules regarding different combinations of.

The listing below shows the syntax of the component declaration. We can divide the code in to sub modules as component and combine them using Port Map technique. Class AdderCell extends Component Declaring external ports in a Bundle called io is recommended val io new Bundle val a b cin in Bool val sum.

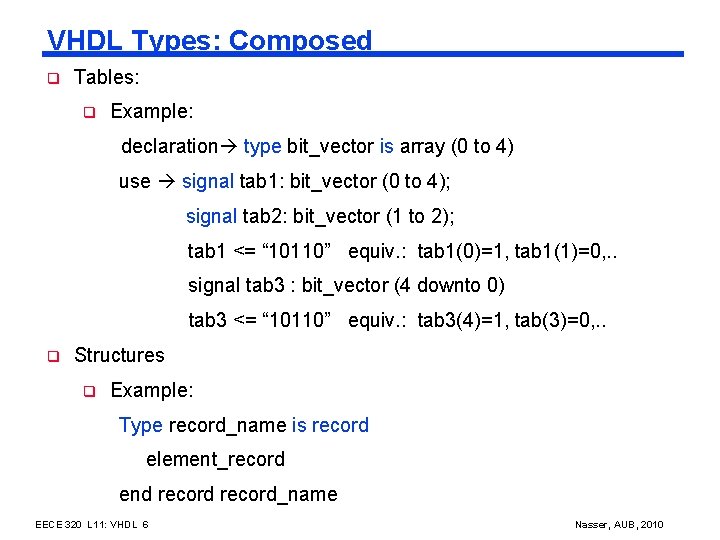

VHDL allows for a hierarchical model layout which means that a module can be assembled out of several submodules. Component instantiation is a concurrent statement that can be used to connect circuit elements at a very low level or most frequently at the top level of a design. Component_declaration component identifier is local_generic_clause local_port_clause end component component_simple_name.

There are several ways to do this. Like in VHDL and Verilog you can define components that can be used to build a design hierarchy. Component component_name is port port list.

Component is a reusable VHDL module which can be declared with in another digital logic circuit using Component declaration of the VHDL Code. Also the keywords end component may be followed by a repetition of the component name. Then we will declare the architecture of the multiplier and define the components using the component keyword in VHDL.

How to use components inside behavioral vhdl. Genericsmay be set via a generic map in an instantiation or a configuration. So now we define components that will be used in the architecture.

1 in Example 1. However in SpinalHDL you dont need to bind their ports at instantiation. A model that describes a circuit as a bunch of interconnected components is qualified as structural.

As generics have a limited scope we can call the same VHDL component multiple times and assign different values to the generic. As you can see a fulladder can be built with the help of two halfadders module1 module2 and an OR gate module3. V HSIC H ardware D escription L anguage A hardware description language HDL used to design electronic systems at the component board and system level.

In a component declaration. This binding must be done with an explicit configuration. VHDL can describe the hierarchical composition of a digital circuit by instantiatingcomponentsorentitiesand by interconnecting them with the aid ofsignals.

Asked 7 years 8 months ago. We use the architecture to create either a functional or structural description of the component. A component represents an entityarchitecture pair.

Every component we design in VHDL requires two separate parts - an entity and an architecture. That usually means in the VHDL files declarative region but you can also define them in packages. Entity of a program can be considered as a component in another program.

VHDL allows models to be developed at a very high level of abstraction. The connections between these submodules are defined within the architecture of a top module. Structural VHDL defines behavior by describing how components are connected.

It specifies a subsystem which can be instantiated in another architecture leading to a hierarchical specification. Every component instantiation must at some point be bound to an actual entityarchitecture pair. The binding of a design entity to a given component may be delayed and may be placed either in the configuration specification or.

This helps to implement hierarchical design at ease. IN std_logic_VECTOR 31 downto 0. A component is just a declaration a kind of empty shell.

Eece 320 Digital Systems Design Lecture 11 Vhdl

Eece 320 Digital Systems Design Lecture 11 Vhdl

Synthesis Issues In Synthesizable Vhdl Descriptions From Vhdl

Synthesis Issues In Synthesizable Vhdl Descriptions From Vhdl

Cryptographic Coprocessor Design In Vhdl Design Logic Projects

Cryptographic Coprocessor Design In Vhdl Design Logic Projects

Pdf How To Use Port Map Instantiation In Vhdl Syntax And Example Sanzhar Askaruly Academia Edu

Pdf How To Use Port Map Instantiation In Vhdl Syntax And Example Sanzhar Askaruly Academia Edu

Vhdl Implementation Of Lookup Table Download Scientific Diagram

Vhdl Implementation Of Lookup Table Download Scientific Diagram

Software Analogies To Vhdl Concepts By Rijul Gupta Medium

Software Analogies To Vhdl Concepts By Rijul Gupta Medium

Component Declaration An Overview Sciencedirect Topics

Component Declaration An Overview Sciencedirect Topics

Synthesis Issues In Synthesizable Vhdl Descriptions From Vhdl

Synthesis Issues In Synthesizable Vhdl Descriptions From Vhdl

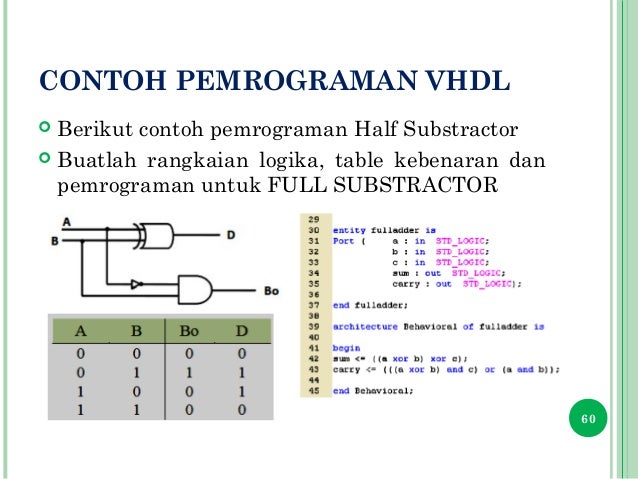

Bahasa Pemrograman Perangkat Keras Vhdl

Bahasa Pemrograman Perangkat Keras Vhdl

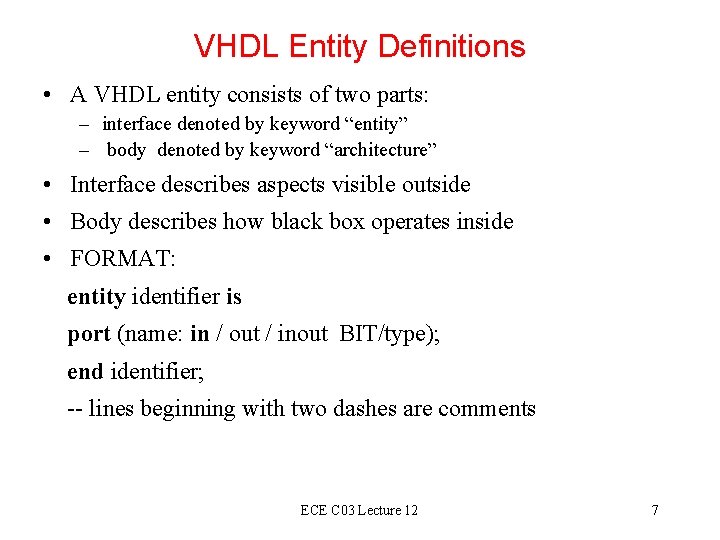

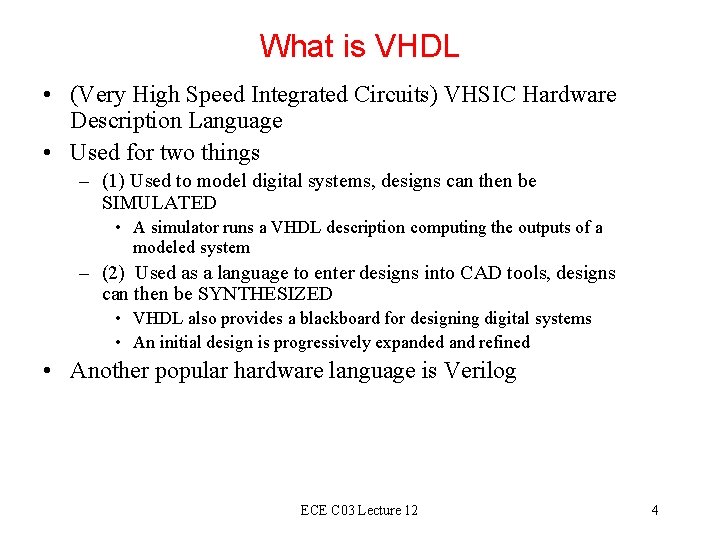

Lecture 12 Introduction To Vhdl Hai Zhou Ece

Lecture 12 Introduction To Vhdl Hai Zhou Ece

Vhdl Structured Logic Design School Of Electrical Engineering

Vhdl Structured Logic Design School Of Electrical Engineering

Bahasa Pemrograman Perangkat Keras Vhdl

Bahasa Pemrograman Perangkat Keras Vhdl

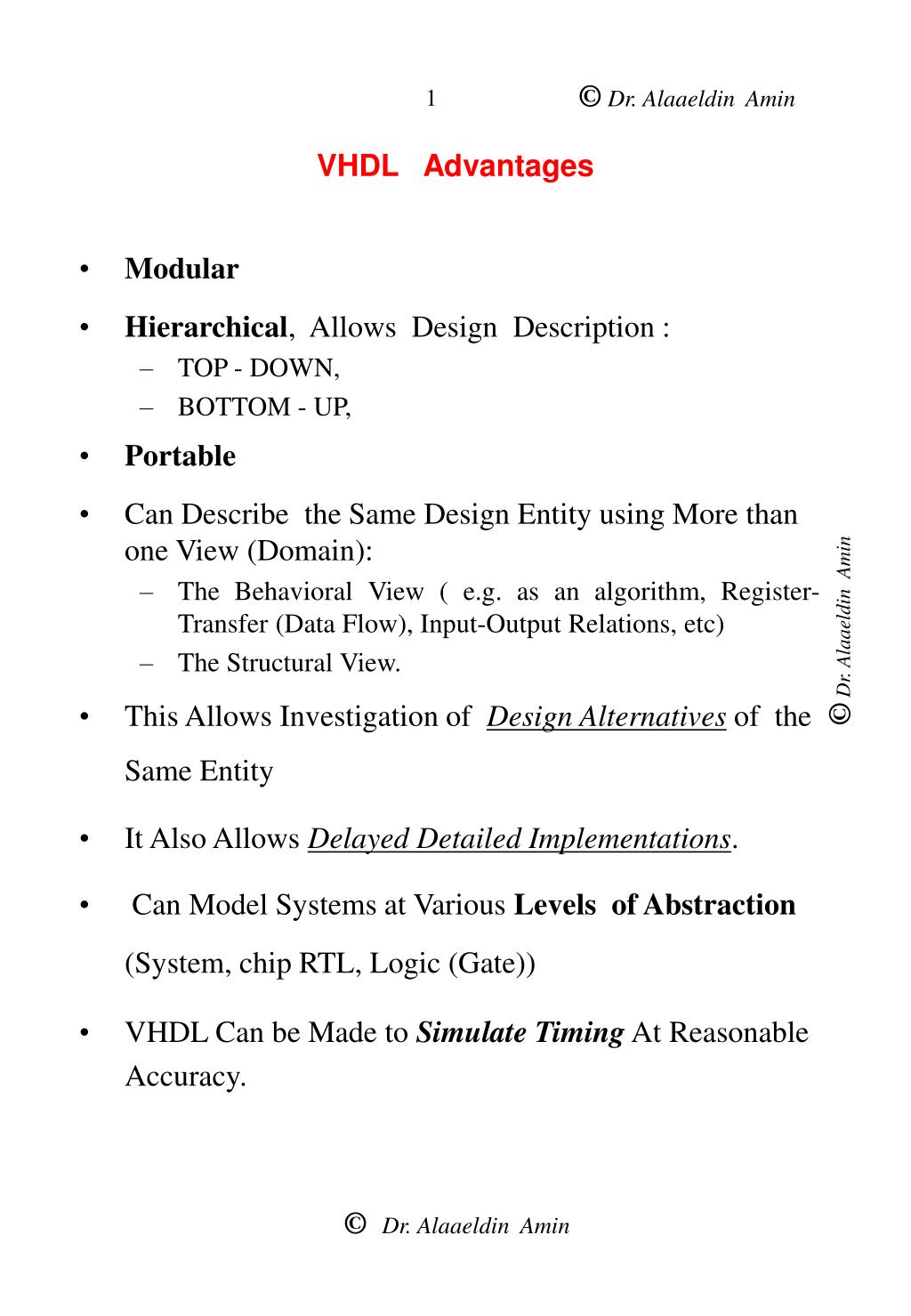

Ppt Vhdl Advantages Powerpoint Presentation Free Download Id 5580546

Ppt Vhdl Advantages Powerpoint Presentation Free Download Id 5580546

Lecture 12 Introduction To Vhdl Hai Zhou Ece

Lecture 12 Introduction To Vhdl Hai Zhou Ece

Vhdl Implementation Of Carry Save Adder Download Scientific Diagram

Vhdl Implementation Of Carry Save Adder Download Scientific Diagram

0 Komentar